# IFAC International Pulse Symposium Budapest, April 1967

# VARIETIES OF COMPUTER - THEIR APPLICATIONS AND INTER-RELATIONSHIPS

### B.R.Gaines

### Standard Telecommunication Laboratories, London Rd., Harlow, Essex -

and Department of Electrical Engineering Science, University of Essex, Colchester, U.K.

### SUMMARY

A major step forward in device technology is being made with the introduction of low-cost integrated circuits and large-scale integration (LSI), the implications of which seem to go beyond those of any previous improvement in computer components. Whereas the transition from vacuum tubes to transistors brought about a tremendous increase in reliability and decrease in physical volume, any increase in physical volume, any increase in physical size was a by-product of these rather than a main effect. What LSI offers is sheer quantity of devices, at a low cost and in a small space - so many devices in fact that the complete processor of a digital computer, or all the active elements of an analog computer, may become a single component.

**w** ...

This paper discusses the impact of LSI on computer systems and computing techniques, and suggests that the major effects will be to make special-purpose computers for specific problem areas very much more attractive, and to blur the distinction between software and hardware - in the sense that computer-assisted design and computer program compiling will merge into a general translation technique from problem specification to both module interconnection (hardware) and variable stored-program (software).

Present theories of computation have been developed either for the minimization of hardware or for the study of programming languages, and are not directly applicable to the hardware/software combination. In particular the inter-relationships between the computer structure and the problem structure are very important considerations to the utility of special-purpose computers, since ease of application is a major requirement in evaluating possible future developments.

It is suggested that the natural system for dealing with the problem of matching computing techniques to problem classes is the theory of maps and their relationships, and in particular the theory of functors over categories of maps developed in homological algebra.

A brief introduction to the application of this theory to computer systems is outlined, which provides a common treatment of the trade-off between sequential implementation of a number of simple operations and parallel implementation of an equivalent single complex operation, and the effect this has on program representation and ease of programming. In particular it provides an explicatum for the ease of operation associated with an analog computer, and suggests an extension of the term 'analog' which preserves this association.

Finally, it is suggested that a natural computer for the real-time problems of navigation and control systems may be based on an incremental digital, DDA-like, arithmetic unit, coupled to a sequential, program-control unit. The pseudo-analog computations of the DDA would be used to generate the complex operations, such as vector rotation and matrix up-dating required in these problems, but its structure need be far simpler than that of previous parallel DDAs because its operations would be varied under program control and used to form an overall computational sequence.

A feasibility study of a modular, programmed incremental computer has been made at STL, and a prototype machine has been developed called the Phase Computer. In the latter part of this paper, the phase computer is described in some detail, and examples are given of a range of basic computations, such as addition, subtraction, multiplication, division, squaring, squarerooting, and rectangular/polar co-ordinate.

Varieties of Computer

1

# VARIETIES OF COMPUTER - THEIR APPLICATIONS AND INTER-RELATIONSHIPS

#### B.R.Gaines

### Standard Telecommunication Laboratories, London Rd., Harlow, Essex and Department of Electrical Engineering Science, University of Essex, Colchester, U.K.

### Introduction

:

e,

### The Impact of Large-Scale Integration

Data-processing and control systems have come to be largely based on two forms of computing technique, epitomized on one hand by the electronic analog computer with its high-gain DC amplifiers and passive networks, and on the other by the general-purpose, stored-program digital computer with its simple processor operating upon binary words and a core-store to hold the lengthy processor control sequence or 'program' involved in any particular computation.

These computers have both been developed to a high level of reliability, small size and low cost, through an evolutionary process dating back at least twenty years. Succesive minor technical advances in materials and components have combined with increasing experience in system design for ease of operation to continually improve their overall performance and utility. One major technical advance significantly improved virtually every performance figure of both types of computer and greatly extended their ranges of application - this was the step from thermionic vacuum tubes to solid state devices.

Now a further major step forward in device technology is being made with the introduction of integrated circuits and large-scale integration (LSI), and the implications of this seem to go beyond that of any previous advance. Whereas the transition from vacuum tubes to transistors brought about a tremendous increase in reliability and decrease in physical volume, any increase in system size was a by-product of these rather than a main effect. What LSI offers is sheer quantity of devices, at a low cost and in a small space - so many devices in fact that the complete processor of a digital computer, or all the active elements of an analog computer, may become a single component.

The benefits of LSI in conventional analog and digital computers are obvious, but not as great as might be expected. The analog computer's reliance on passive components to establish the nature and accuracy of its computations limits the direct impact of LSI since these components are not amenable to micro-miniaturization (except for high-frequency, short-term computation). The digital computer's reliance on an extensive core-store to carry both program and data also limits the direct impact of ISI since the store cost is by far the major proportion of the overall computer cost.

There are regions of computation where extensions of the conventional machine organization will continue to be effective, or become very much more effective. For example, at high frequencies in radio and navigation systems, the improved gain-bandwidth characteristics of modern integrated circuit operational amplifiers makes active filtering techniques based on precision thin-film passive networks very attractive. Similarly in large facilitytype computer systems which must be flexible enough to perform virtually any computation, the best utilization of LSI may be to replace core memory with very fast, but volatile, integrated arrays, which can be replenished regularly from disc back-up stores.

#### Beyond Software and Hardware

These particular examples apart, the real impact of LSI may be summed up colloquially as a swing from 'softwarebased ' computation towards 'hardware-based' computation. The present emphasis on programming a computation rather than fabricating a computer stems from two causes - one being the early isvelopment of digital computers when the vacuum tube processor was massive, unreliable and produced vast quantities of heat, so that it made good sense to minimize the processor hardware, and utilize a program stored on drum or in core to achieve computational power - the other being the initial prime need for general-purpose computing facilities shared by large, inhomogeneous populations of users. So that extreme flexibility was the major objective. Now that integrated circuits are available to make the processor small, cheap and reliable, and there is an increasing demand for special-purpose computers dedicated to particular functions in specific equipment, these considerations are no longer universally applicable.

A computation represented by a 'program' or bit-pattern in a core-store may be expressed just as effectively as

the interconnection pattern of a set of circuit modules. Once such a configuration is established the resultant computer is 'special-purpose' in the same way that a particular program for a conventional, stored-program machine is 'special-purpose,' but the step from a problem specification to an interconnection pattern may be as 'general-purpose' as required, i.e. an extensive range of different computations may be established.

It is important to note that specialpurpose, hard-wired machines need not lack 'flexibility', in the sense of being able to perform a variety of computations and switch between them as required. It is only necessary that all the computations be included in the problem specification. Since the required computation must be selected in some way, it might be expected that a specification involving extreme flexibility would best be met by a conventional organization involving selection through a program in core-stors !

The wiring of modules to form specialpurpose computers enables full advantage to be taken of the hardware offered by ISI, and is particularly attractive in realtime computation where the special-purpose machine will generally be faster, cheaper and smaller than a stored-program, generalpurpose machine. Typical problem areas where such machines are of immediate interest are automatic control, aircraft and marine navigation systems, product quality monitoring and air-traffic control. In these areas one may expect the conventional instrument and associated special-purpose computer to merge, probably so completely that any separation between them will be conceptual rather than real. Data-processing techniques will become part of established system technology, and the 'computer' will only rank as a separate unit in the sense than an IF-strip is a unit at present.

Since the design aids for any future system engineering may be expected to contain the equivalent of 'high-level' languages for problem specification, and the appropriate 'compilers' for turning a problem statement into the implementation of a solution, the 'programming' of a special-purpose machine will not necessarily appear different from that of a generalpurpose machine today. 'Programming' in itself only implies a clear, unambiguous problem statement, not a sequential implementation, and seems a suitable word to apply to both special-purpose and general-purpose machines. The distinction between 'hardware' and 'software' implementations will decrease in importance, however, since it will be optimization procedures within the compiler which determines the combination of module-interconnection and stored-program to be used in realizing a particular computation.

### The Place of Incremental Computing

In these real-time, special-purpose computers, the standard digital computer processor with an arithmetic unit capable of implementing a few simple operations such as data-transfers, COMPLEMENT, ADD, SHIFT, AND, etc., will not necessarily be optimal. To minimize the length of program sequence required and to simplify the problem of implementing a program on the machine, it is best if the elementary processor operations correspond to the natural operations in the problem statement. In numerical data-processing, addition, subtraction, multiplication and division are generally required, but these are insufficient basic operations in navigational systems where trignometric operations such as vectorrotation are of equal importance, or in adaptive controllers and filters where matrix manipulations are also required.

Since these real-time problems are generally generated by dynamical systems specified by differential or difference equations, it would not be surprising if the 'natural' operations were best generated by computational techniques for solving such equations. The computation of trignometric and hyperbolic functions, and the solution of matrix up-dating equations is indeed very simple on the electronic analog computers and on incremental digital computers such as the DDA. As previously discussed, the conventional analog computer has little to gain from LSI, but the 'counting' techniques adopted in the DDA are ideal for realization by arrays of standard digital gates, and multiple DDA integrators will be readily accomodated in a single package.

The 'conventional' parallel DDA in itself, however, is capable only of the complete, single-configuration solution to a particular problem; the sequential decoding of the general-purpose digital computer's 'program' is completely lacking. A DDA set up for a given problem may be regarded as a special-purpose processor without any sequential programming capability, and, on the grounds of coding theory, one would expect it to be wasteful of hardware and inflexible in operation. This has been acceptable in the past because DDAs have been used for the high-speed, continuous solution of differential equations, not for the sampled-data, discrete operations of non-differential, numerical data processing.

The DDA and the conventional digital computer may be seen as opposite extremes in the approach to problem solution - the one adopting an entirely parallel decoding of the problem statement into a single operation, and the other a highly sequential decoding into a multitude of minor operations. The optimum approach would be expected to be somewhere between these two, with an operation set selected according to the distribution of common operations in the problem class to be solved, and sequential statement of particular problems in terms of these operations.

Thus, a very attractive real-time data-processing system might be based on the use of the incremental, pseudo-analog computations of the DDA to generate a family of computing operations natural to navigational and adaptive control problems, together with the sequencing control operations of the digital computer microprogram to combine the DDA operations in a branching structure which generates the problem solution. In this mode the DDA would be used to solve final-value problems, rather than to give a continuous output, and externally it would appear as a normal arithmetic unit with operations such as ROTATE the vector in registers X and Y through the angle 0, together with more usual operations such as, ADD, SQUARE, TRANSFER, MULTIPLY, DIVIDE, and so on.

A feasibility study of a modular, programmed incremental computer has been made at STL and a prototype machine has been developed called the Phase Computer [1]; this study is reported in the latter part of this paper. Although this machine is complete in itself, however, as are the 'analog computer' and the 'digital computer; and has important applications as a selfcontained unit, it is presented here primarily as an example of the possibilities for new forms of computing system with the increasing availability of low-cost integrated circuits and LSI.

### Problems of Future Computer Engineering

The combination of incremental digital computing with sequential control used in the phase computer is only one of many possible examples of computing configurations. Further examples of configurations at this level of simplicity are:- the combination of analog and digital computers in a 'hybrid' system [2]; the combination of analog integrators and digital stores and sequencers in Schmid's SADC [3]; combination of parallel binary processing, digital/analog multiplication and analog addition in the Ambilog 200 [4]; the combination of analog filters under analog control in model-reference adaptive controllers [5]; the combination of analog filters under digital control in adaptive line equalization [6]; the use of transfluxor-driven resistive networks for matrix inversion in conjunction with a digital computer [7] - the list could be greatly extended and is growing at an increasing rate.

The number of machines using mixed computing techniques at present, however, is neglible compared with the number of conventional, stored-program, digital computers, processing parallel binary words with standard logic configurations. The extension of the processors of these machines by the addition of multiple hardware accumulators, index-registers, priority-interupt systems, autonomous data transfer units, hardware multiply/divide and variable-length arithmetic units, and high-level language features such as hardware DO-loops, does not essentially aiffer from the extension by adding analog processing capabilities, for example. The function of an index register is to make it simpler and faster the process data-arrays - the function of an analog section may be to speed and simplify matrix inversion or vector rotation; in all cases the

function of the extension is to increase speed, decrease overall cost, or simplify the programming of a particular problem for the computer.

3

Thus, the structural and functional design of future computing systems will raise problems which, at present, are far more the province of the computer linguist than the electronic engineer. The judicious implementation of closed subroutines which may be called as complete entities in a variety of programs has its parallel in the synthesis of modules with a particular function to be built into a variety of systems. The synthesis of problem-oriented languages and associated compilers has its parallel in the development of families of modules peculiarly suited to navigation or control problems, and the associated design aids for interconnection specification.

In so far as problem areas may be distinguished, there appear to be four of especial importance:-

(1) Computing techniques - the interrelationships between various forms of data-representation and between the means for implementing computations in these various representations.

(ii) Partitioning - the modular elements

which can become single LSI circuits and

are compatible one with another.

(iii) Sequential/parallel - the

(11) Sequential/parallel - the relationship between the performance of a computation as a single operation or as a branching sequence of simpler operations, and the hardware/time tradeoffs involved.

(iv) Ease of Implementation- the relationship between the problem specification and the hardware/software of the computer system.

These main areas alone encompass information-processing system function, organization, implementation and utilization, and no distinct separation is possible between them. Although a comprehensive treatment of these problems cannot be given at present, it is possible to establish a theoretical framework for their study, and analyse present computing systems within it. The following section outlines a general theory of computation based on the concept of functors between categories of mappings, and illustrates this with comparative examples from various forms of computer.

#### · Theory of Computation

#### Maps Between Operators

Although automata theory provides the necessary terminology and mathematical objects for the analysis and synthesis of sequential circuits to perform defined functions, the main emphasis of its present development is on minimizing the hardware (in some sense) required for the computer to perform a particular computation, rather than matching the computer to a class of computations and maximizing the ease of programming. The natural system for dealing with these problems is the theory of maps and their relationships

The fundamental problem of computation may be stated in abstract - given a map, f, from a domain, D, to a range, R, (the computation), to establish mappings, i, from I (a sub-set of computer input configurations) onto D, and o from  $\theta$  (a sub-set of computer output configurations) onto R, such that there exists a map p belonging to P (the set of computer operations or programs) which makes the diagram -

<u>р</u> д ( Ι\_ 10 R

fully commutative. That is, to any object, 6, in D there corresponds δI<sup>-1</sup>po ≕ one in I and ôf, the computer gives the correct result.

Since D could be the set of state/ input pairs of a finite automaton and R the set of next-state/output pairs, this definition includes computer simulation of any finite automaton. Equally D = R might be the state-space of a dynamical system and f an infinitesimal time-displacement, in which case p might be the corresponding analog computer up-dating of the statevariables represented by voltage levels.

The requirement for commutativity in the above diagram indicates that a computers function is to simulate another system exactly in its input/output behaviour -that is, in Wiener's terminology, to be cybernetically equivalent to the system. In general, the computer is required to simulate not just one system but any member of a large class of systems, and the transformation, f, may be taken as one member of a category of maps, F. The task of programming the computer is then to find a map from the category of programs, P, onto that of systems,  $F - T: P \rightarrow F$ , together with suitable input and output codings, such that diagrams of the type above are commutative. By regarding the input/output codings as maps in T between the identies for I,  $\Theta$ , D and R, this can be subsumed into a single map, T, which in the present context is, trivially, a functor from programs to systems.

The structure developed so far is concerned only with the overall transformations implemented by the system and the computer, not with the possible structures of these tranformations - it has been assumed that there is no overlap between the domains of any maps and the ranges of others (except for identities), and hence products of maps are undefined - if p, p' belong to P, then  $pp' = \varphi$ . The crucial feature of computing to be examined, hence in which complex however, is the manner in which complex transformations are built up as (branching) sequences of simple operations, and the structure must be extended to include this.

Consider the computer as a device

which can implement any one of a set of operations, S, from and to computer configurations or states. Each operation may be regarded as a set of maps from sub-sets of computer configurations, and the category of all these maps will be denoted by  $\sigma$ . Consider the free semigroup generated by concatenation of maps belonging to  $\sigma$ ,  $\Sigma$  - this is the totality of all sequences of operations executable by the computer.

Any member of  $\Sigma$  may obviously be regarded as a program for the computer, but the definition of a program must be wider than this to take in the possibility of branching. A program is defined to be a sub-set of  $\Sigma$ , p, such that if  $\alpha$ ,  $\alpha^{*}$ , contained in  $\Sigma$ , belong to p, and -

α

φ

ai<sub>a</sub> = α'i<sub>α</sub> = then

4

that is, the domains of any maps in p are disjoint - under these conditions p is itself a map. If p consists of only one member of  $\Sigma$  then it is a non-branching program.

### Analog and Non-Analog Operations

The map T:  $P \rightarrow F$  from programs to systems may now be regarded as a map from some sub-set of  $\Sigma$  onto F. However consider the non-branching program p = st (s, t belonging to  $\sigma$ ), such that -

$$\mathbf{pT} = \mathbf{f}$$

$$f = stT.$$

but it possible that -

then

#### ≠ (sT)(tT), f

because these two terms are undefined. That is, there may be no operations within the system which are equivalent to those within the computer - examples are obvious, data-fetches, summation of power series to form cosine of an angle, and so on.

If T is a functor not just from some sub-set of E but from the generating category of  $\Sigma$ ,  $\sigma$ , then it is reasonable to call the computer an 'analog computer' for the systems F. In this case, to every computer operation s belonging to S, there corresponds a system transformation, g,

such that g sT =

that is the computer operation, s, and the system transformation, g, are analogous.

The electronic analog computer is an 'analog computer' in this sense for linear dynamical systems represented in stateform Ŷ

$$I = \underline{A} \underline{Y}$$

the scalar products of the row vectors of A with the column vector Y each being represented by a summing integrator. Similarly, a digital computer with the (three address) operations ADD, TWOS-COMPLEMENT, MULTIPLY, is an 'analog computer for the operations associated with a certain finite number field, but one with the operations, ADD, TWOS-COMP., SHIFT, is not, although it is capable of

#### executing the same programs.

The importance of the 'analog' relationship is in its effect upon ease of programming. To program a computer to simulate a system, the exact nature of the system must be communicated to the computer is some coded form. If an arbitrary code is used and there are a large number of possible systems, then the task of the programmer in encoding the problem and the task of the computer system into decoding this into computer operations are both very difficult. If the systems to be simulated have some natural structure so that all system operations may be represented as a sub-set of the free semi-group generated by some basic system operations, then the task of the programmer is simplified by basing the code on the concatenation of symbols for these operations - that is, giving the programmer a problem-oriented language. Similarly, the task of the computer system (its compiler) is simplified if the code is a direct specification of the computer operations - that is, 'machine-code'. If the computer is an 'analog computer' for the systems then these two forms of coding coincide.

One important property of the analog representation is its implication for intermediate results in a computation. The system operation f may be satisfactorily represented by the computer program p. It may happen that f factorizes into two, or more, system operations -

$f \simeq gh$

and p may probably also factorize, but there may be no factorization of p such that - - rs

|       | Р |   | 10            | , |        |                |

|-------|---|---|---------------|---|--------|----------------|

| where | g | Ξ | $\mathbf{rT}$ |   |        |                |

| and   | h | Ŧ | $\mathbf{sT}$ | , | unless | $\mathbf{the}$ |

computation is 'analog'. Thus, intermediate results in the system may be unobtainable from the computer. This illustrates one of the fundamental problems in replacing an electronic analog computer facility with a digital one. Even though an optimization routine, for example, may be stated in an initial/final value form, the intermediate values may be important in discovering its unforseen defects.

### Hardware Implications

There is in general no unique factorization of a set of system operations into a free semigroup generated by basic system operations. The selection of a particular set of basic operations on which to base an 'analog' computer will depend on a number of factors. The cost of the hardware necessary to implement the corresponding computer operations and sequence them appropriately is one. The time taken to perform the operations, whether the overall mean time or maximum time, is another. In small special-purpose machines the sequencing system may be the most expensive item, and minimization of the length of program is a suitable design criterion for factorizing the system

#### operations.

D

So far the sequencing of computer operations has been treated in a somewhat artificial manner by defining a program as a sub-set of  $\Sigma$  consisting of maps disjoint domains. Thus, if the set of basic computer operations is  $\Sigma:(p,q,r,s,t)$ , then a program might consist of four possible sequences -

## pattq, paqtq, paqrq, paqrt

5

- these maps have different domains and one possible form of sequencing is to test the initial computer configuration to determine in which domain it lies and then implement the corresponding sequence. Alternatively the sequences might be written as a continually branching structure -

$$\rightarrow$$

" $\downarrow_{0}$   $\not \land_{r}$   $\not \land_{t}$

in which there is a choice point after virtually every operation.

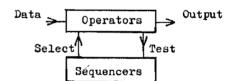

The sequencing of operations in a branching program can thus be represented as implementation of an operation plus a test to determine the next operation. A test is itself a map from the range of a map representing computer operations to the set of operations itself, and hence constitutes a feedback loop. The basic computer structure may be represented -

### Illustration by Digital Computer/DDA Comparison

Consider the solution of a typical linear differential equation on the stored-program digital computer, for example -

$$\mathbf{x} + \mathbf{x} + \mathbf{x} = \mathbf{0}$$

with boundary conditions x(o) = a,  $\dot{x}(o) = b$ . Define a second state-variable

so that the equation becomes -

$\dot{x} = y$ , x(o) = a $\dot{y} = -y-x$ , y(o) = b.

These may be solved reasonably accurately by simple rectangular integration provided time is quantized sufficiently finely, t = nh, where h is small, giving the equations -

$$x(n+1) = x(n) + hy(n)$$

$$y(n+1) = y(n) - hy(n) - hx(n)$$

.

On a large machine with floating-point arithmetic a simple sequence could be written immediately for these equations. On a small machine two sources of difficulty would be apparent - a multiplication by h is required, and h is very small so that at least double-length precision is required in the additions.

The multiplication by h can be simplified by making h a negative power  $h = 2^{-N}$ of 2

say.

so that the multiplication may be implemented by an arithmetic right shift of N places. This has interesting implications for the multiple length addition, for if the shift is such as to move the number through one full word then the addition operation only affects the lower half of the double-length result, apart from a possible overflow (or underflow - the possibility of negative numbers causes some minor complications which have an effect on the coding of numbers in different DDA registers)into the upper half.

Thus the computation may be reduced to addition or subtraction of the upper registers holding x and y, to or from the lower registers, detecting and storing overflows, and using these to update the upper registers. This is a sequential computation which bears little resemblance to the original dynamical equation, and the computer operations are not analogs of the system operations. When a large number of state-variables are involved the computation is very time-consuming, even though the tricks of multiplication by shift and split double-length working have already speeded it up considerably.

There are two basic techniques for speeding up the computation. The first utilizes the fact that adding in to the lower part of the double-length words, detecting any overflow and setting the overflow increment to the upper word can be made a single operation. This is the basis of the early drum DDAs, to update each integrator by a single operation (although they generally create errors by adding the overflows straight into the upper words in arbitrary sequence so that some results are up-dated when they are added in, others are not). The second technique is to duplicate the hardware required for this operation and update all the integrators together - this is the basis of the parallel DDAs [14,15,16].

The first technique corresponds to taking some sub-set of  $\Sigma$  obeying the axioms of a 'program' and setting up a basic computer operation equivalent to the transformation realized by this program. The second technique is more interesting as it demands that parts of the computation be performed in parallel and hence have no sequential interdependence. This requires that the map corresponding to the program may be expressed as a Cartesian product of maps, which is reasonable in the case of analog simulat-ion in the DDA, but may be difficult to determine in other, more general, cases[17].

#### Conclusions from the Theory

It has been possible in the previous section to give only a superficial outline of a potentially rigorous approach to the design of complex computer systems. It does, however, provide a common treat-ment of the trade-off between sequential implementation of a number of simple operations and parallel implementation of a single complex operation, and the effect that this has on program representation and ease of programming. In particular it provides an explicatum for the ease of operation associated with the analog computer, and suggests an extension of the term 'analog' which preserves this association.

6

The most important conclusion to be drawn from the theoretical treatment is that intuitive considerations of what makes for ease of design and problemsolving in data-processing and control systems do have a firm foundation, and that the system 'costs' in terms of speed, price, flexibility and ease of use may be treated in a common framework. Such a treatment is essential if the hardware/ software 'compilers' [18] of tommorrow's computing systems are to become a reality.

This concludes the general and theoretical sections of this paper. In the final section, the Phase Computer is described in some detail. It exemplifies both the modular, LSI-dependent, programming-through-interconnection approach dicussed in the first section, and prov-ides an interesting computing structure for analysis using the techniques outlined in the second section - at the incremental, or DDA, level the computations may be seen as the repetition of long sequences of simple operations to build up more complex computations, whilst at the 'sequencer', or overall function, level the computations may be seen as providing a variety of complex operations directly available.

#### The Phase Computer

### Introduction

The particular problem which first stimulated the development of the phase computer was the realization of the leastsquares smoothing and prediction equations for automatically tracking radar targets [19,20]. Previously these had been imple-mented on a general-purpose digital computer, but it was desired to use them in circumstances where no conventional computer was available, or economically feasible, and the simplest and cheapest, special-purpose equation solver was required.

The tracking equations involve addition, subtraction, multiplication, division, squaring, square-rooting, sine/cosine generation and inverse sine/cosine resolution, so that they encompass a very wide range of arithmetic operations. They may be reagarded as Kalman-Bucy equations for optimum system identification [21], and hence any system for their solution has immediate relevance to adaptive control problems. The data-rate in both surveillance radars and control systems is fairly low (typically between 0.1 and 100 samples/second) and incremental computing

.

techniques offered the possibility of solving the equations with very simple hardware. Since the data was already in sampled-form, it was attractive to decrease the cost still further and add to the flexibility of the computer by executing the computations as a sequence of simpler operations.

Apart from its sequential, programmed operation, the phase computer has one other feature not found in previous para-11el DDAs, and that is the use of unidirectional counters throughout the computer rather than the bi-directional, up/down counters of the DDA. This feature, which not only decreases the cost but also greatly simplifies the operation, is made possible by use of the 'phase counting' principle in which stored quantities are represented as the <u>difference</u> in the counts contained in two counters. Incrementing both counters does not change the stored value - incrementing one and not the other either increases or decreases the stored value, according to which counter is taken positively (the Store) and which negatively (the Reference). The use of this technique is not uneconomic in hardware, because one counter generally acts as Reference to a number of others.

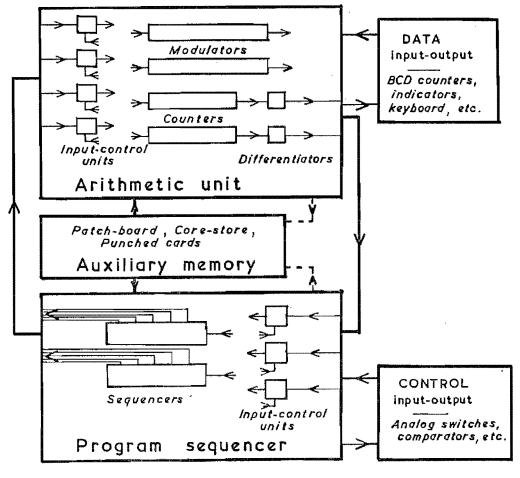

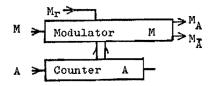

A block-diagram of the phase computer

Varieties of Computer

is shown in Figure One below. It has a conventional four-part structure, consisting of arithmetic unit, program sequencer, auxiliary storage, and input/output channels, but the arithmatic unit is incremental digital, the sequencing section is very extensive and may operate several concurrent programs, and the auxiliary storage in the laboratory prototype machine is realized entirely through a patch-board.

In terms of the abstract structural analysis of the preceeding main section; the counters and modulators are devices for implementing arithmetical operations; the input-control units in the upper section are devices for selecting these operations; the sequences are devices for implementing a sequence of operations; the input-control units in the lower section are devices for selecting this sequence; and the differentiators are devices for detecting conditions on which to branch the program sequence.

A detailed description of these elements and their functions is given in the following sub-sections, followed by a description of their use in simple processors for various computations, together with some examples of input/ output devices for analog and numeric data.

Figure One - Phase Computer Schematic

8

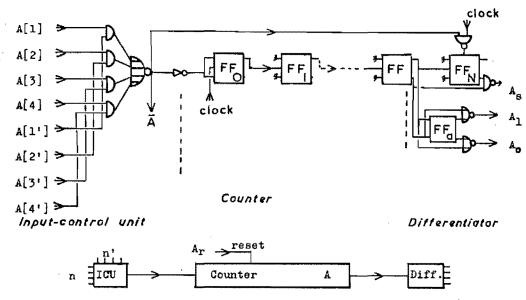

Figure Two - Counter, Control and State-detection

#### Counters and Modulators

The active storage registers of the phase computer are unidirectional, synchronous, binary counters which, at a clock pulse, increment by unity if their INPUT line is ON, and reset to zero if their RESET line is ON. Although the overall counters operate synchronously, they may be internally asynchronous, as shown in Figure Three (reset omitted from logic diagram).

One peculiarity of the counters is that they have  $2^N + 1$  states, achieved using N+1 flip-flops, so that the fractional binary number stored in the counter may take the full range of values from zero though unity, but the zero state and maximum state are identical in the counting cycle which has only  $2^N$  stages. This enables counters used as storage registers to take a complete range of values, but does not lead to an additional state causing difficulty in some computations.

Figure Three - Modulator

If the proportion of ON logic levels; on the INPUT line of the counter is considered as the input variable, then the counter may be regarded as a discrete version of an analog integrator, in that its stored count will be proportional to the input times the period of integration. The counter alone, however, lacks an output in the form of its input - the integral is available as a binary number rather than an incremental sequence.

An incremental sequence in which the proportion of ON logic levels is equal to the fractional binary number stored in a counter is obtained, as shown in Figure Three, from a modulator element which adds (through full-adders) the number in the counter to that in a register (D-type flip-flops) and outputs the overflows.

Figure Four - 4-way Sequencer

In order to maintain accuracy when the count in the counter is changing, the quantity added into the register is the mean of the present count and the coming next count(closed trapezoidal integration). The modulator has input lines for controlling additions to the register and for resetting it.

### Sequencing Computations

By connecting the outputs of modulators to the inputs of counters, pseudoanalog computing loops may be set up in the arithmetic unit of the phase computer and used to generate operations which are difficult to realize with parallel digital arithmetic. In general, however, the loops used will be far simpler than those of conventional DDAs, the majority of counters generating ramps rather than nonlinear functions, and the basic computational operations realized in this way, such as multiplication, division, addition and subtraction, are combined in programmed sequences to yield more complex overall behaviour.

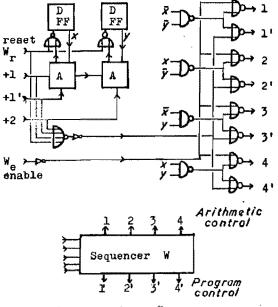

The essence of programming in all computers is the control of the interconnections between processor elements by logic levels on CONTROL lines. The inputcontrol unit, shown in Figure Two, is a gate enabling processor connections to be controlled - it implements the function:

### A = A[1]A[1']+A[2]A[2']+A[3]A[3']+A[4]A[4'],

and may be regarded as a digital selector switch in which the INPUT line A[j] is switched through to the output if the CONTROL line  $A[j^*]$  is ON alone. In some applications two, or more, CONTROL lines may be required for each input.

Input-control units placed at the inputs of phase computer counters enable them to be interconnected with modulators in several alternative patterns, any one of which may be selected by activating the appropriate CONTROL lines. A sequencer unit, shown in Figure Four, is used to activate the CONTROL lines corresponding to different interconnection patterns in a programmed sequence. It is made up of a small register, to each of whose states there corresponds an OUPUT line which is ON when the register is in that state. These OUTPUT lines are connected to the counter CONTROL lines so that different states of the register give rise to different computing configurations.

An adder and gating enables the state of the sequencer to be reset to zero or incremented by any amount (generally unity for normal operation and two for a branch) - reset taking precedence over incrementing. All the OUTPUTS of the sequencer are turned OFF for the single clock pulse at which it is incremented or reset. A second set of OUPUTS is also made available for control of input-control units to sequencers and these are not turned OFF as the sequencer changes. None of the sequencer outputs is ON unless its ENABLE input is ON.

The signals causing the sequencers to change their states, corresponding to steps

and branches in the program, are obtained from digital 'differentiators' which give an ouput for the clock pulse following that in which the counter enters a certain state - in particular, the zero  $(A_0)$ , and mid-range state  $(A_1)$ . The outputs of the differentiators are used to change the states of Sequencers when certain counters accumulate pre-determined counts during a computation.

The use of these various elements and their interconnection to perform computations is best made clear by example, and the following soction describes phase computer configurations for a wide variety of basic arithmetic operations.

### Unsigned Arithmetic Operations

9

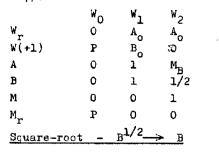

A small phase computer processor might consist of three counters, A, B, C, one or two modulators, L, M, a 3-way sequencer, W, and associated input-control units and differentiators. The sequencer would be used to switch the inputs to counters either ON or OFF, or to the outputs of modulators, and the connections associated with each state of the sequencer can be specified by the signals at the counter inputs. The outputs from the differentiator will be used to change the state of the sequencer or reset counters, and this program control can be specified by the changes that may occur, and their causes, in each state of the sequencer.

Thus any particular computation may be specified completely by a table of the following form:-

| Sequencer | <br>State -  | ۷o | ۲  | W2 |

|-----------|--------------|----|----|----|

|           | Reset -      | 0  | ٨_ | A  |

|           | Advance-     | Р  | Bo | 0  |

| Counters  | <br>A input- | 0  | ı  | 1  |

|           | B input-     | 0  | 1  | 1  |

|           | C input-     | 0  | 0  | 1  |

|           | C reset-     | P  | 0  | 0  |

This table corresponds to data-transfer, or reproduction of the quantity stored in counter B in counter C, assuming that counter A initially is at zero and that the computation is initiated by a pulse, P. In the zeroth state of the sequencer,  $W_0$ , all counter inputs are OFF - this is the passive state. The pulse P resets counter C to zero and advances the sequencer to its first state  $W_1$  in which the inputs to counters A are both ON (written as 'l'). When counter B overcounts to zero, the differentiator output B causes the sequencer to advance to state  $W_2$  in which the input to counter C is also ON. Finally the sequencer returns to the passive state W when counter A overcounts back to its initial state of zero.

The overall effect on the counters in this computation can be determined from the quantities transferred in during each state of the sequencer. If the fractional binary number initially in counter B is  $\beta$ , then the quantity transferred in to bring the count in B to zero is  $1-\beta$ . Thus when the sequencer advances to  $W_{2}$ , A contains  $0 + (1-\beta) = 1-\beta$ , B contains  $\beta + 1-\beta = 1$  $\equiv 0$  (complete cycle), and C still contains zero. During the sequencer state  $W_{2}$  the quantity required to return counter A, containg  $1-\beta$ , to zero is  $\beta$ . Hence finally A contains  $(1-\beta) + \beta \equiv 0$ , B contains  $0 + \beta = \beta$ , and C contains  $0 + \beta = \beta$ .

This computation illustrates the phase counter principle, for if the quantity stored in B is taken to be the difference in counts between counter A and counter B then this is invariant provided the inputs to the two counters always receive the same signal - it will be noted from the table that this is so. Since counter A starts and finishes in zero, it has no initial or final effect on the stored quantity which may be taken as the fractional binary number in B.

The table may be abbreviated -

|                         | ۷o | ۳ı | ₩2 |

|-------------------------|----|----|----|

| ₩ <sub>r</sub><br>W(+1) | o  | A_ | A  |

| W(+1)                   | Р  | B  | 0  |

| A                       | 0  | 1  | l  |

| В                       | 0  | l  | l  |

| C                       | 0  | 0  | 1  |

| ° <sub>r</sub>          | Р  | 0  | 0  |

### Data Transfer - B → B, C

If the initial resetting of C is omitted then this becomes addition of the quantity in B to that in C -

|            | Wo  | ۳ı     | ₩2             |

|------------|-----|--------|----------------|

| Wr         | ໐ັ  | Ā      | A <sub>o</sub> |

| ₩(+1)      | P   | В      | 0              |

| A          | 0   | ĩ      | 1              |

| В          | 0   | l      | 1              |

| C          | 0   | 0      | 1              |

| Addition - | в 🔶 | B, B+C | → C            |

Subtraction is a simple variant on this in which C counts during  $W_1$  rather than  $W_2$  -

|                         | ۷o | ۳ı | ₩2 |

|-------------------------|----|----|----|

| W <sub>r</sub>          | õ  | A_ | A  |

| ₩ <sub>r</sub><br>\(+1) | Р  | в  | ບັ |

| A                       | 0  | ı  | 1  |

| В                       | 0  | 1  | 1  |

| C                       | о  | l  | 0  |

|                         | _  | _  |    |

Subtraction -  $B \rightarrow B$ ,  $C-B \rightarrow C$

If C initially contains  $\gamma$ , since the count added whilst the sequencer is in W<sub>1</sub> is 1- $\beta$ , the final total in counter C is  $\gamma \neq (1-\beta)$  $\equiv \gamma - \beta$ .

For multiplication, B is connected to the modulator, M, and its input is OFF throughout the computation so that its state does not change. The ouput of M,  $M_{\rm B}$ , is a sequence of logic levels in which the proportion of ON levels is equal to  $\beta$ , the

fractional binary number in B. This is connected to the input of C between C entering zero and A returning to zero, a period proportional to the quantity in C,  $\gamma$  - so that the final quantity in C is  $\gamma\beta$ :-

10

| Þ            | Wo   | ۳ı    | W <sub>2</sub>             |

|--------------|------|-------|----------------------------|

| Wr           | ໐ັ   | A     | A <sub>o</sub>             |

| ₩(+1)        | Р    | c     | o                          |

| A            | 0    | ı     | 1                          |

| В            | 0    | 0     | 0                          |

| C            | 0    | 1     | M <sub>B</sub>             |

| М            | 0    | 0     | 1                          |

| Mr           | Р    | 0     | 0                          |

| Multiplicati | on - | в 🛶 в | $C \times B \rightarrow C$ |

<u>Multiplication - B  $\rightarrow$  B, C x B  $\rightarrow$  C Division is realized in a similar</u>

fashion, except that the connections to A and C are reversed, so that during the sequencer state,  $W_2$ , the quantity  $\gamma$  has to be supplied to A from the source M<sub>B</sub>, and hence the quantity transferred to C during this period is  $\gamma/\beta$ :-

| •                       | ۷o      | ۳ı   | ₩2                  |  |

|-------------------------|---------|------|---------------------|--|

| ₩ <sub>r</sub><br>W(+1) | 0       | A    | A                   |  |

| W(+1)                   | P       | C    | 0                   |  |

| A                       | 0       | l    | м <sub>в</sub>      |  |

| В                       | 0       | 0    | 0                   |  |

| C                       | 0       | 1    | 1                   |  |

| М                       | 0       | 0    | 1                   |  |

| M <sub>r</sub>          | P       | 0    | 0                   |  |

| Division                | <br>в 🛁 | ≻ В. | $C/B \rightarrow C$ |  |

Squaring the quantity in B offers the first example of a modulator being used to generate a nonlinear function through connection to a changing counter. The output from the modulator M during  $W_{\eta}$ , whilst B counts from its initial value up to zero would be -

$$\int_{\beta}^{1} u du = (1-\beta^2)/2$$

if the modulator and counter inputs were ON together. By connecting the counter input to a source whose proportion of ON logic levels is 1/2 (a toggling flip-flop), the number of clock intervals for B to return to zero is doubled, and so is the above integral. This quantity is counted into A, so that at the end of W<sub>1</sub> A contains  $1-\beta^2$ , and the remainder to be counted in  $\frac{1}{2}$ during W<sub>2</sub> is  $\beta^2$ , which also enters B:-

| - 2            | ₩o       | ۳ı             | W2             |

|----------------|----------|----------------|----------------|

| W <sub>r</sub> | o        | A              | A <sub>o</sub> |

| ₩(+1)          | P        | ເັ             | 0              |

| A              | 0        | м <sub>в</sub> | 1              |

| В              | 0        | 1/2            | 1              |

| М              | 0        | l              | 0              |

| Mr             | 1_       | 0              | 0              |

| Squaring       | <u> </u> | <u>B</u>       |                |

Taking the square-root of the quantity in B is performed in a similar fashion

Rectangular/polar co-ordinate conversion requires an additional modulator, L, coupled to counter A. The vector (x,y) in Cartesian co-ordinates, whose components are stored in counters B and C respectively, is to be converted to  $(r,\theta)$ , polar co-ord-inates stored in the same locations. First, during W<sub>1</sub>, 1-y is transferred to A, and then counters A and B are cross-coupled with the modulator output M<sub>B</sub> at the input of A, and the inverted modulator output L<sub>T</sub> at the input of B. This may be represented by the differential equations -

$$\frac{dx/dt}{d(1-y)/dt} = x$$

so that

$$x + x = 0$$

,

corresponding to rotation of the vector (x,y). This ceases when A returns to 0, in which event the y-component has become zero and the x-component in B is equal to  $r = (x^2 + y^2)^{1/2}$ . The quantity accumulated in counter C during W<sub>2</sub> is proportional to the angle of rotation<sup>2</sup>,  $\theta$ , in units such that one right-angle corresponds to unity in the counter, and the conversion from radians is accomplished by counting from a source in which the proportion of ON logio levels is  $2/\pi$  (obtained from a modulator with constant, hard-wired input):-

|                                 |        | -                 |                 |

|---------------------------------|--------|-------------------|-----------------|

|                                 | Wo     | Wl                | ¥2              |

| Wr                              | 0      | A                 | Ao              |

| W(+1)                           | P      | C_                | 0               |

| A                               | 0      | ı                 | МВ              |

| В                               | 0      | 0                 | Т. <sub>д</sub> |

| C                               | 0      | 1                 | 2/π             |

| Ľ                               | 0      | 0                 | 1               |

| М                               | 0      | D                 | 1               |

| Rectangular/Polar               | Co-ore | linate            | Conversion      |

| $(B^2 + C^2)^{1/2} \rightarrow$ | ► B ,  | tan <sup>-1</sup> | (B/C) → C       |

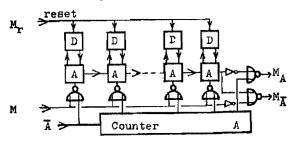

# Signed Arithmetic Operations

The preceeding sub-section has dealt with arithmetic operations on positive quantities only. Signed numbers are represented in the counters in twos-complement form with the sign bit reversed so that zero quantity is represented by the midrange value in the counter. The sign bit is not connected to the adder in the modulators, but is used to gate the normal and inverted outputs of the modulators to give an additional output proportional to the magnitude of the twoscomplement binary fraction in the counter; for counter B connected to modulator M this output is designated M<sup>a</sup><sub>B</sub>.

11

Computations with signed quantities are generally a little more complicated than with unsigned since branching is generally necessary to take the signs into account. These may be accomplished, in the basic computations considered so far, by means of a 5-way sequencer using both ADVANCE +1 and ADVANCE +2 inputs.

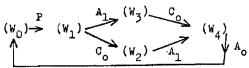

For example, multiplication is done by a configuration corresponding to the table:-

|                         | ۷o | W              | W2  | W <sub>-x</sub>    | W <sub>4</sub> |

|-------------------------|----|----------------|-----|--------------------|----------------|

| ₩ <sub>r</sub><br>W(+1) | ٥  | ດີ             | ວັຼ | A                  | A              |

| W(+1)                   | P  | °              | 0   | ¢,                 | 0              |

| W(+2)                   | 0  | A <sub>1</sub> | A   | ໐ັ                 | 0              |

| A                       | 0  | 1              | ı   | 1                  | l              |

| В                       | 0  | 0              | 0   | 0                  | 0              |

| Q                       | 0  | 1              | l   | 1                  | 1              |

| D                       | 0  | Be             | MB  | $M_{\overline{B}}$ | Вв             |

| D <sub>r</sub>          | P  | ດັ             | ៰៑  | ໐ັ                 | ວ້             |

Signed Multiplication -  $B \times C \longrightarrow D$

If the quantity in C is positive then  $C_0$  comes on before  $A_1$  and the sequence is  $W_0 W_1 W_2 W_4 W_0$ , whereas if it is negative  $A_1$  comes on first and the sequence is  $W_0 W_1 W_3 W_4$ , so that the branching structure is -

The computation may be checked out by considering each of the four possible sign combinations in turn - for example, it the quantity in B,  $\beta$ , is negative, and so is that in C,  $\gamma$ , then the sign bit of B is  $B_S = 0$ , and the path of computation is  $W_0 \ W_1 \ W_3 \ W_4$ . The quantities accumulated in counter D are - 1/2 in  $W_1$ ,  $\beta\gamma$  in  $W_2$  and zero in  $W_4$ , so that  $\delta$ , the final quantity in D is given by -

$$\delta + 1/2 = 1/2 + \beta \gamma + 0$$

,

and thus  $\delta = \beta \gamma$ . Similarly the other possibilities may be checked.

Addition, subtraction and data transfer are performed with the 3-way sequencer configurations outlined previously, except that  $B_1$  replaces  $B_2$  because of the modified twos-complement representation Division, squaring, vector rotation, and so on, are all readily performed with signed quantities, but the configuration used will vary with the overall computation, since several operations on different registers will generally be performed at the same time.

#### Input/Output Devices

Since most applications of the phase computer are in real-time data-processing, control and display systems, input and output has been an important design consideration and facilities for BCD/binary conversion and analog/digital conversion fit naturally into the structure of the machine.

Any counter in the computer is potentially capable of being set directly with a binary number, and also of being read out directly from the condition of its flip-flops. It is more convenient, however, to use special interface counters for binary input and output, and transfer from these to the required register using a counting sub-routine. The internal counters, used in computations, can then have a very simple structure with a minimum of connections. Interface counters having a BCD representation may then be used for automatic decimal to binary, and binary to decimal, conversion.

Input and output of analog data on many parallel channels is performed in the phase computer by a single digital/analog convertor, plus analog track/hold and comparator units for each channel. The D/A convertor generates a ramp by outputting the quantity in a cycling counter in analog form, and this is compared with sample analog inputs to control the counting of other counters which act as input data registers, or sampled by track/ hold units at the output which are themselves controlled from counters acting as output data registers [1].

### Summary and Conclusions

The topics treated in this paper have ranged through the impact of LSI on computing systems, the development of an integrative theory of computation that enables hardware and software problems of all forms of computer to be treated in a single, coherent framework, and a specific example of a novel form of computer in which incremental arithmetic and programmed sequential computation are combined. It is convenient in this final section to take these topics in the reverse order.

The phase computer is a modular, digital, data-processing and control system, in which many of the advantages of analog and digital computers are combined through the use of an incremental digital arithmetic unit under program control. The incremental processor enables pseudo-analog computing loops to be established so that complex operations, such as division, square-rooting, rectangular/polar/hyperbolic co-ordinate transformations, and so on, may be performed with the same speed and simplicity as simpler operations, such as additfacility enables complex computations to be performed as a sequence of elementary operations, and hence overcomes the inordinate hardware demands of previous parallel

### incremental computers.

12

The speed of the incremental processor in performing simple operations is less than that of a parallel digital arithmetic unit because of the counting technique used, and the disparity becomes greater with increasing precision in computation. This factor is very much decreased in computations where a number of operations may be carried out at the same time. At present, with a 4 Mcs clock rate, operations can be carried out with 10-bit precision and accuracy in times of about 250 microseconds, and with 12-bit precision and accuracy in about 1 millisecond. These speeds and accuracies have proved ample for a large class of dataprocessing and control applications, and enable advantage to be taken of the economy and simplicity of phase-computing.

Applications investigated to date include: area coverage systems for aircraft navigation based on VOR/DME beacons; direct readout of latitude and longitude for hyperbolic marine navigation based on differential transmission paths; sweep generators for PPIs in surveillance radar systems; marker/vector generators with rectangular/polar co-ordinate conversion facilities in PPI consoles; automatic tracking of radar targets by least-squares smoothing and prediction for small radar systems; identification of process parameters for purposes of adaptive control; and on-line product quality monitoring with reject-rate prediction.

Apart from its intrinsic advantages, the phase computer is also of interest as an example of a computing system in which the range of basic operations includes those peculiarly required in specific problem areas, such as vector rotation in navigation systems, and matrix up-dating in identification systems. The relationship between the computer operations and the structure of the system it is programmed to simulate may be formalized algebraically in terms of natural mappings between categories of maps. Such a theory of computation gives a formal explicatum for the concept of an 'analog computer', and makes clear the reasons why a computer bearing this relationship to a class of systems is simple to use.

The phase computer is also of interest because it is an all-digital, modular system based on modern integrated circuits. There are only five basic modules in the computer - counters, modulators, inputcontrol units, sequencers and differentiators. They may be fabricated with standard integrated circuits and utilize fully the high packing density devices, such as multi-bit counters and adders. By their simplicity and uniformity of structure, and their few interconnections, the modules and module-systems are eminently suitable for large-scale integration.

The phase computer is, however, only one particular example of the possibilities opened up by modern, low-cost integrated circuits and the impact of LSI on computer organization. In an accompanying paper [18] R.A.Shemer discusses more general arithmetic and sequencing units, and their application to both programmed DDAs and to conventional general-purpose digital computation. Such modules may operate in several modes and implement various computing techniques within the same computational cycle. Indeed, the distinctions between techniques become arbitrary in such a structure, since parallel DDA operations may always be treated purely algebraically as series expansions of the functions generated and are most conveniently analysed in this way.

It should be possible at the present state of knowledge to dispense with hard and fast distinctions between analog, digital, incremental, and hybrid, computers, and so on, and treat the technology of data-processing and control in a unified and coherent manner. The main obstacles to progress in this direction are our lack of detailed knowledge about computing techniques in themselves - of their relationships to hardware, and particularly to what constitutes a viable module both from the viewpoint of the computer engineer and from that of the component engineer - and last, but by no means least, of the interrelationship between the hardware/software combination which is the computer, and the structure of the systems it is required to simulate and the problems it is required to solve.

#### <u>Acknowledgements</u>

I am grateful to many colleagues in ITT for discussions and suggested applications of the phase computer - in particular to Mr.P.L.Joyce of STL who built the first laboratory prototype machine.

## References

- [1] Gaines, B.R., Joyce, P.L., Phase Computers, Proc. 5th Int.Congr.AICA, Lausanne, August 1967.

- [2] Korn, G.A., Korn, T.M., <u>Electronic</u> <u>Analog and Hybrid Computers</u>, McGraw Hill, 1964.

- [3] Schmid, H., Sequential Analog-Digital Computer (SADC), AFIPS FJCC <u>27</u>(1) 1965.

- [4] Hagan, T.G., Treiber, R., Hybrid Analog/digital Techniques for Signal Processing Applications, AFIPS SJCC <u>28</u> 1966.

- [5] Donalson, D.D., Kishi, F.H., Review of Adaptive Control System Theories and Techniques, in <u>Modern Control Systems</u> <u>Theory</u> McGraw Hill, 1965.

- [6] Lucky, R.W., Techniques for Adaptive Equalization of Digital Communication Systems, Bell Syst.Tech.J. 45(2) 1966.

- [7] Karplus, W.J., Howard, J.A., A Transfluxor Analog Memory Using Frequency Modulation, AFIPS FJCC <u>26</u>(1) 1964.

- [8] Clifford, A.H., Preston, G.B., <u>The</u> <u>Algebraic Theory of Semigroups</u>, Vols. I and II, AMS 1961 and 1967.

### Varieties of Computer

[9] Ljapin, E.S., <u>Semigroups</u>, AMS 1963.

- [10] Eilenberg, S., MacLane, S., General Theory of Natural Equivalences, Trans. AMS <u>58</u> 1945 231-294.

- [11] Cartan, H., Eilenberg, S., Homological Algebra, Princeton U.P. 1956.

- [12] Northcott, D.G., <u>An Introduction to</u> <u>Homological Algebra</u>, Cambridge U.P.1962

- [13] Freyd, P., <u>Abelian Categories</u>, Harper Int.Ed.1966.

- [14] Bradley, R.E., Genna, J.F., Design of a One-Megacycle Iteration Rate DDA, AFIPS SJCC <u>21</u> 1962.

- [15] Mitchell, J.M., Ruhman, S., The TRICE - A High Speed Incremental Computer, IRE Nat.Conv.Rec. Pt.4 1958.

- [16] Goldman, M.W., Design of a High Speed DDA, AFIPS FJCC 1965 <u>27</u>(1).

- [17] Conway, M.E., A Multiprocessor System Design, FJCC 1963.

- [18] Shemer, R.A., A Hybrid-Mode Modular Computing System, IFAC Symposium on Pulse Techniques, Budapest 1968.

- [19] Simpson, H.R., A Method of Processing Radar Data to Obtain Position, Velocity and Turn Information, RRE Memo.1924 1962.

- [20] Mellberg, K., Experience from Automatic Tracking in ATC, IEE Conf.Pub. No.28, Symposium on ATC Control Systems Engineering and Design.

- [21] Kalman, R.E., Bucy, R.S., New Results in Linear Filtering and Prediction Theory, Trans.ASME March 1961.

### B. HRUZ:

You mentioned the problem of identification of a system in automatic control. In what do you see the advantages of the DDA or incremental techniques in identification modelling systems if it is borne in mind that the use of A-D and D-A converters is needed and this complicates the system. This is interesting in respect to speed, cost, reliability, etc.

B. R. GAINES: This is the kind of point which I think we would very much like to bring up in discussion, because your question raises a large number of quite distinct points on the interface between a computer, Digital to Analogue and Analogue to Digital, with incremental techniques. Of course we have applied them to quite simple controllers, PID controllers, where the output has been some kind of stepping device, a valve driven by a stepping motor, and we have had a digital actuator. And again, the cheapest form of A to D converters are counting techniques which ideally interface with the system. So I do not think one should complain that the interface to the computer presents difficulties, in fact one of the main reasons for using this kind of computational technique is that we can get very much cheaper interfaces.

Within the computer itself, identification is one of those words once again which cover a multitude of things. There is identification e.g. in terms of steepest descent techniques. And here, one has within the computation generally a large number of multiplications and has a feedback loop outside, of a performance criterion with which one is tending to match it. We have had comparisons between various techniques, the analogue ones, the incremental ones and so on, and once again the incremental techniques show up very well as soon as one gets away from the stage where the GP machine is capable of counting within a computation.

Within the GP machine it always comes to a factor of time. If you have got the time to go through a program loop to do the computation necessary for steepest descent, then this is more often than not the best way to go about it. It is quite an extensive computational loop, the more inputs you have got, the more parameters you have got, the more times you have got to go around the loop, and once you get up to something like ten parameters then you really are taking up of a lot of GP time. This is the kind of level at which one wants to go to parallel techniques. If you go to parallel techniques you have got a choice between trying to put several general purpose processors on to it. Each of these will require a program and are rather expensive. If you go to analogue elements, the steepest descent identification requires analog multipliers which are expensive and unreliable.

In the other areas of identification, there has been no attempt so far to use identification methods in a discrete state space, say with models of processes as Markov transitions, probabilistic transitions between states. This has all been written out in theory, but has never .

been implemented in practice, except, on some simulations which in themselves have never got very far because it is a very expensive thing to simulate. This is the kind of thing which one can now do, using inceremental techniques, and provided the elements are cheap enough. We have it performing for example in our laboratory. where we have put special hardware onto a GP computer, so the arithmetic unit of the computer can look like a special purpose DDA element. This is for simulation purposes, so we can, in fact, simulate networks of several thousands of integrator elements, without building more than one special purpose unit. This really is the problem area of what advantages does one gain. Are there other ways of gaining the same advantages which are going to come first, or are we in fact avoiding the question of these ways at the moment with DDA-s, and just going to find that there is a bigger way coming along with variations on GP machines? Or are we really on to something which is going to become increasingly important within control systems? I think this should form part of this afternoon's discussion.

After a recess, the Chairman, J. Hatvany, asked B. R. Gaines to introduce the Plenary Discussion.

l

B. R. GAINES: The first point which I would like to raise is

probably relevant to the members of the Technical Committees of IFAC who are here. When we run a conference, then by the very nature of the editing process we have a very lop-sided view of the whole field. If I had put in a paper for this conference on GP computers and their applications to automatic control, Dr. Hatvany would have returned it to me and said "It is a very pleasant paper, but completely irrelevant to the conference" and equally if I had put in a paper in which I said that we had been working with DDA-s for about ten years and we tried to apply them to control systems and it had been completely fruitless, he would have said "Hard luck, but this is a very negative paper" and returned it to me. So the only papers we tend to get, are by people who are proselytes for DDA-s and other such systems. And I wonder whether I should take the opportunity of giving the papers which I never sent in because I knew they would be rejected? And trying to put the case for the GP computer, for the poor old analogue computer which we all tend to sneer at, and for the various techniques which are appearing nowadays. We all introduce the DDA through Large Scale Integration, and say: "Oh, the DDA-s are going to make a come-back because LSI's going to make integrated circuits very much cheaper." This of course, is affecting almost anybody building any system whatsoever, and it is reasonable to look at the GP computer and say: "Well, it has got a very simple processor and a massive core store, and all we are really making at the moment is volatile memories, so

they are going to have to go on using those

magnetic cores, and they do not know how to make multiprocessor machines and so they are not going to be able to take very much advantage of Large Scale Integration." In a way this is true, but equally there is a very large number of people with vested interests in the GP computer. And they are really the ones who generated Large Scale Integration. They can not be doing this just to pass themselves out of the market.

I was in New York at the IEEE International Convention recently, and from Texas Instrument there was a device coming out which was a read-only memory, with a cycle time of 20 nanoseconds, in which at present they have got about a thousand bits on a slice but they are aiming by 1973 to be supplying in production quantities, one with about 300 thousand bits per slice. Now this is a pretty substantial program size, so that for many of the applications we have been discussing, applications to automatic control, where programs are fixed, we are going to be able to use this for quite a number of jobs. Let us take for example a PDP 8 computer. The processor there, using Texas 74N series, takes up about 200 packages. This is probably equivalent to about 1000 to 1500 gates. So in three of four years' time that is going to be 3 or 4 packages coupled to this type of read-only memory, and we have got a complete computer, a very powerful machine, which can have as many data registers, as many volatile registers as we would like, in a few slices, at a very low cost. This can be a very powerful device. One important advantage of this read-only memory, is that the programming is done externally by blowing internal links, by in fact burning through the metallization. So they are offering a GP component imposing no real constraints on the computer manufacturer, putting out something which has got a very large market, and costs very little. We certainly will see very cheap GP machines becoming available, and we have got a whole army of programmers, and quite a lot of experience in using these machines. So if we are putting forward DDA-s this is one thing we are fighting against. In another area, at the Spring Joint Computer Conference there were several papers on hybrid techniques, and the most interesting ones were using D/A converters as computer elements in very much the same way as we have been proposing incremental modules. They have been taking the D/A converter, which once again is very amenable to Large Scale Integration, and seeing how to interconnect large numbers of these to form a computing system. This is a device where you put in a digital number on one channel, and get what is really a variable analogue weight, in fact a digitally controlled potentiometer, where you can put analogue signals through several of these, and control the gates digitally. Adage, for example, are using this in a very nice graphical display which plots a complete line in 4 microseconds and can plot about 5 thousand lines flicker-free on a display and rotate them in 3 dimensions, or more if one really wants it. So here, once again we have an example of a computer technique.

What is tending to happen with these is exactly the same as happened with DDA-s. People are calling them by all kinds of odd names so as to pretend to their own companies that they have invented something new. They are generalizing them and building up a complete system, and they are in fact restricting the applications by trying to use these elements throughout the system. If one, in fact, examines the variety of computer techniques available now, then it has become very very much larger during the last few years. The GP computer, the analogue computer have been coming down in price, and equally there have been a large number of new techniques.

I think "new" is probably a bad word here, for every one of the techniques which one sees and which one gets excited about, one can count back to about 1950, and can find there. In fact, if one looks at the history of the analogue computer and the digital computer and the DDA, one arrives back inevitably at the Second World War, one finds the Bush mechanical differential analyzer being used for ordnance calculations, one finds ENIAC transformed into EDSAC under the influence of von Neumann, so that the stored program digital computers have been generated in about 1946, and one also finds the operational amplifier which is the basis of the analogue computer, being made available as a high stability reliable component at about much the same time. If one looks at the growth of these up to about 1960, the growth patterns are very similar. From then onwards we have got an ever increasing growth, according to at least an exponential law, particularly in the stored program digital computer, especially as it went from scientific to commercial use. The analogue computer seems to have fallen off fairly level, and the DDA looked as if it was just going to droop away into nothingness.

Looking through the previous conference proceedings, one can find that the conferences specifically on incremental techniques are around the 1960-s, so that there was about an eight years' gap, eight years in which there has been very little communication among people working in this field. To some extent, one might say that this has indicated a lack of interest in DDA-s. But the lack of communication is really because they have been applied largely to military uses. However, when examining the possibility of incremental techniques having some place in future systems, we must be aware of the competition here, and certainly a strong competition from a new generation, it is not the 5th generation or the 4th generation, it is an offshoot virtually --- a micro-program special purpose computer but using the standard GP techniques, taking advantage of Large Scale Integration. And this is certainly a very strong competitor in the control field and in putting forward the advantages of the DDA one should also really consider exactly the same problems proposed to this type of machine and look at the concurrent advantages.